## mercury

# Cobalt 57610/58610 Single or dual LVDS digital I/0

6U VPX boards with Virtex-6 FPGA

Ideal for control and data capture applications

- Provides 32 pairs of LVDS digital I/O

- LVDS is popular for high-speed video, graphics, and general-purpose computer buses

- User-configurable Virtex-6 FPGA

- Rugged, conduction-cooled option for military and avionics applications

### The 57610 and 58610 are members of the Cobalt<sup>®</sup> family of highperformance 6U OpenVPX boards based on the Xilinx Virtex-6 FPGA. They consist of one or two 71610 XMC modules mounted on a VPX carrier board.

The 57610 is a 6U board with one 71610 module while the 58610 is a 6U board with two XMC modules rather than one. These models include one or two general-purpose connectors for application-specific I/O.

#### **FEATURES**

- 32 or 64 bits of LVDS digital I/O

- One or two LVDS clocks

- One or two LVDS data valid

- One or two LVDS data suspend

- Supports LXT and SXT Virtex-6 FPGA

- One or two DMA controllers move data to and from system memory

- Up to 2 or 4 GB of DDR3

- PCI Express (Gen. 1 & 2)interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O to the carrier board

- Ruggedized and conduction-cooled versions available

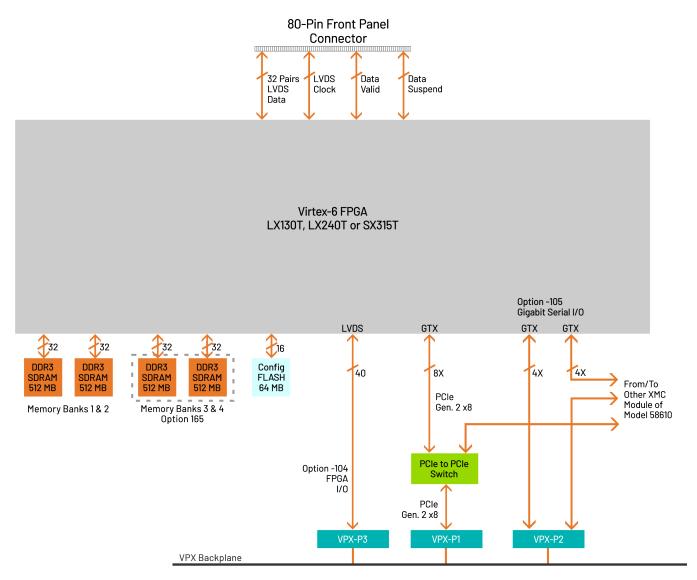

#### 57610 BLOCK DIAGRAM

Click on a block for more information.

Block diagram 57610 shows half of the 58610. All resources are actually double of what is shown except for the PCIe-to-PCIe Switch and provides 24 LVDS pairs from the 2nd FPGA to VPX-P5.

#### THE COBALT ARCHITECTURE

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's interface. The 71610 factory-installed functions include 32-bit acquisition and generation IP modules, to support either input or output functions, respectively.

IP modules for DDR3 SDRAM memories, a controller for all data clocking, a test signal generator, and a PCIe interface complete the factory-installed functions and enable the 71610 to operate as a complete turnkey solution without the need to develop any FPGA IP.

#### **EXTENDABLE IP DESIGN**

For applications that require specialized functions, users can install their own custom IP for data processing. The GateFlow FPGA Design Kits include all of the factory-installed modules as document source code. Developers can integrate their own IP with the factory-installed functions or use the GateFlow kit to completely replace the IP with their own.

#### **XILINX VIRTEX-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/ decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

#### ACQUISITION IP MODULE

These modules can be configured for digital input mode by the setting of one or two jumpers. In this case, the board accepts input data Clock and input Data Valid signals. This supports a continuous input Clock with data accepted only when the Data Valid line is true. The board can optionally generate a Data Suspend output signal indicating that these models are no longer capable of accepting data. The board accepts 32 bits from the front panel connector or from a non-board test signal generator.

Each IP module has an associated memory bank for buffering data in FIFO mode or for storing data in transient capture mode. Memory banks are supported with DMA engines for easily moving input data through the PCIe interface.

#### **MEMORY RESOURCES**

The hardware architecture supports up to four or eight independent 512 MB memory banks of DDR3 SDRAM. The board is always configured with 1 GB of memory (Banks 1 and 2).

In addition to the factory-installed functions, custom userinstalled IP within the FPGA can take advantage of the memories for many other purposes. For customers who need more memory to support their IP, Banks 3 and 4 can be optionally added for a total of 4 GB.

#### PCI EXPRESS INTERFACE

These models include an industry-standard interface fully compliant with PCI Express Gen. 1 and 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the board.

#### **GENERATION IP MODULE**

These modules can be configured for digital output mode by setting one or two jumpers. In this case, the board generates output data Clock and output Data Valid signals. This supports a continuous output Clock with data valid only when the Data Valid line is true. The board can optionally accept a Data Suspend input signal to halt data generation when the destination device is no longer capable of accepting data.

One or two linked-list controllers allows users to generate 32bit digital words out through the front panel LVDS connector from tables stored in either on-board or off-board host memory. Parameters including length of table, delay from software trigger, table repetition, etc. can be programmed for entry. Up to 64 individual link entries can be chained together to create complex output patterns with minimum programming.

#### READYFLOW

Mercury provides ReadyFlow<sup>®</sup> BSPs (Board Support Packages) for all Cobalt, Onyx, and Flexor products. Available for both Linux and Windows, these packages:

- Provide a path for quick start-up through application completion

- Allow programming at high, intermediate and low levels to meet various needs

- Are illustrated with numerous examples

- Include complete documentation and definitions of all functions

- Include library and example source code.

ReadyFlow BSPs contain C-language examples that can be used to demonstrate the capabilities of Cobalt, Onyx, and Flexor products. These programming examples will help you get an immediate start on writing your own application. They provide sample code that is known to work, giving you a means of verifying that your board set is operational.

#### **COMMAND LINE INTERFACE**

The Command Line Interface provides access to pre-compiled executable examples that operate the hardware right out of the box, without the need to write any code. Board-specific hardware operating arguments can be entered in the command line to control parameters: number of channels to enable, sample clock frequency, data transfer size, reference clock frequency, reference clock source, etc.

The Command Line Interface can be used to call an example application from within a larger user application to control the hardware, and parameter arguments are passed to the application for execution. Functions that control data acquisition automatically save captured data to a pre-named host file or are routed to the Signal Analyzer example function for display.

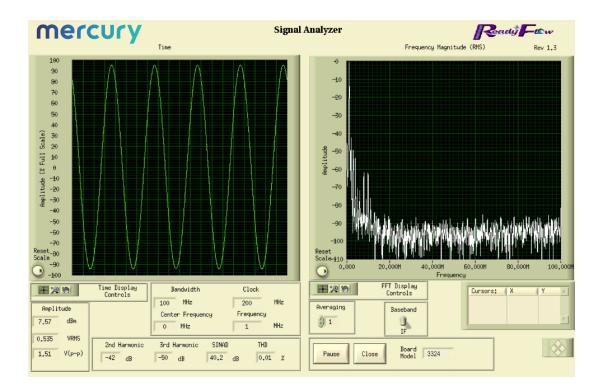

#### SIGNAL ANALYZER

When used with the Command Line Interface, the Signal Analyzer allows users to immediately start acquiring and displaying A/D data. A full-featured analysis tool, the Signal Analyzer displays data in time and frequency domains. Built-in measurement functions display 2nd and 3rd harmonics, THD, and SINAD. Interactive cursors allow users to mark data points and instantly calculate amplitude and frequency of displayed signals.

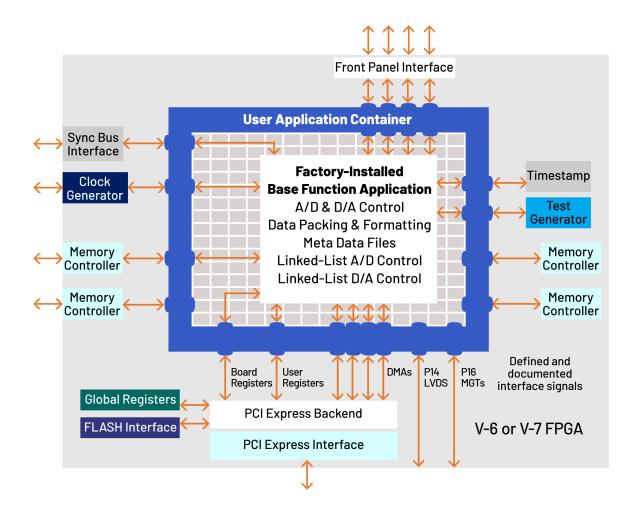

#### GATEFLOW

The GateFlow<sup>®</sup> FPGA Design Kit (FDK) allows the user to modify, replace and extend the standard installed functions in the FPGA to incorporate special modes of operation, new control structures, and specialized signal-processing algorithms.

The Cobalt (Virtex-6), Onyx (Virtex-7), and Flexor (Virtex-7) architectures configure the FPGA with standard factory-supplied interfaces including memory controllers, DMA engines, A/D and D/A interfaces, timing and synchronization structures, triggering and gating logic, time stamping and header tagging, data formatting engines, and the PCIe interface. These resources are connected to the User Application Container using well-defined ports that present easy-to-use data and control signals, effectively abstracting the lower-level details of the hardware.

#### The User Application Container

Shown below is the FPGA block diagram of a typical Cobalt, Onyx or Flexor module. The User Application Container holds a collection of different installed IP modules connected to the various interfaces through the standard ports surrounding the container. The specific IP modules for each product are described in further detail in the datasheet of that product.

The GateFlow FDK provides a complete Xilinx's ISE or Vivado project folder containing all the files necessary for the FPGA developer to recompile the entire project with or without any required changes. VHDL source code for each IP module provides excellent examples of how the IP modules work, how they might be modified, and how they might be replaced with custom IP to implement a specific function.

#### FRONT PANEL CONNECTIONS

The XMC front panel provides an 80-pin digital input/output connector. The front panel also includes two LEDs.

**SPECIFICATIONS**

2.5 V compliant

2.5 V compliant

pair, 2.5 V compliant

57610: Single LVDS Digital I/0; 58610: Dual LVDS Digital I/0

Front Panel Input/Output (1 or 2)

Data Lines: 35 LVDS differential pairs (32 pairs supported in factory-

Data Valid: One LVDS differential pair,

Data Suspend: One LVDS differential

installed functions), 2.5 V compliant

Clock: One LVDS differential pair,

### USR 1 and USR 2

LEDs: The yellow LEDs indicate Input /Output operating status.

## Field Programmable Gate Array (1 or 2)

- Standard: Xilinx Virtex-6 XC6VLX130T

- Optional: Xilinx Virtex-6 XC6VLX240T or XC6VSX315T

#### Custom I/O

- Option -104: Provides 20 LVDS pairs between the FPGA and the VPX P3 connector, 57610; P3 and P5, 58610

- Option -105: Supports serial protocols by providing a 4X gigabit link between the FPGA and VPX P2, 57610; orone 4X link from each FPGA to P2 and an additional 4X link between the FPGAs, 58610

#### Memory (1 or 2)

- Standard: Two 512 MB DDR3 SDRAM memory banks (1 and 2), 400 MHz DDR

- Option 165: Two 512 MB DDR3 SDRAM memory banks (3 and 4), 400 MHz DDR

#### **PCI Express Interface**

PCI Express Bus: Gen. 1 or 2: x4 or x8

#### Environmental

Standard: L0 (air-cooled)

- Operating Temp: 0° to 50° C

- Storage Temp: -20° to 90° C

- Relative Humidity: 0 to 95%, non-condensing

Option -702: L2 (air-cooled)

- Operating Temp: -20° to 65° C

- Storage Temp: -40° to 100° C

- Relative Humidity: 0 to 95%, non-condensing

Option -763: L3 (conduction-cooled)

- Operating Temp: -40° to 70° C

- Storage Temp: -50° to 100° C

- Relative Humidity: 0 to 95%, non-condensing

#### Physical

Dimensions:

- Depth: 171 mm (6.717 in.)

- Height: 100 mm (3.937 in.)

Weight: VPX Carrier: 110 grams (3.9 oz)

#### ORDERING INFORMATION

| Model | Description                                              |

|-------|----------------------------------------------------------|

| 57610 | Single LVDS Digital I/O with<br>Virtex-6 FPGA -6U VPX    |

| 58610 | Dual LVDS Digital I/O with two<br>Virtex-6 FPGAs -6U VPX |

| Options                          | Description                                                                                                         |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| -062                             | XC6VLX240T FPGA                                                                                                     |  |

| -064                             | XC6VSX315T FPGA                                                                                                     |  |

| -104                             | LVDS I/O between the FPGA<br>and P3 connector, 57610; P3<br>and P5 connectors, 58610                                |  |

| -105                             | Gigabit link between the FPGA<br>and P2 connector, 57610;<br>gigabit links from each FPGA<br>to P2 connector, 78610 |  |

| -155*                            | Two 512 MB DDR3 SDRAM<br>Memory Banks<br>(Banks 1 and 2)                                                            |  |

| -160                             | Two 8 MB QDRII+ SRAM<br>Memory Banks (Banks 3 and 4                                                                 |  |

| -165                             | Two 512 MB DDR3 SDRAM<br>Memory Banks<br>(Banks 3 and 4)                                                            |  |

| -702                             | Air-cooled, Level 2                                                                                                 |  |

| -763                             | Conduction-cooled, Level 3                                                                                          |  |

| *This option is always required. |                                                                                                                     |  |

This option is always required.

Contact Mercury for compatible option combinations.

#### **DEVELOPMENT SYSTEMS**

Mercury offers development systems for Cobalt products. They come with all pre-tested software and hardware ready for immediate operation. These systems are intended to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Cobalt boards. Please contact Mercury to configure a system that matches your requirements.

#### FORM FACTORS

Cobalt products are available in standard form factors including 3U VPX, 6U VPX, PCIe, and XMC. The Cobalt Model 71610 XMC (LVDS Digital I/O with Virtex-6 FPGA) has the following variants:

| Model |                                                     |

|-------|-----------------------------------------------------|

| 52610 | 3U VPX board (single XMC with optical/backplane RF) |

| 57610 | 6U VPX board (single XMC)                           |

| 58610 | 6U VPX board (dual XMC)                             |

| 71610 | XMC module                                          |

#### LIFETIME SUPPORT FOR COBALT PRODUCTS

Mercury offers worldwide customers shorter development time, reliable, rugged solutions for a variety of environments, reduced costs, and mature software development tools. We offer free lifetime support from our engineering staff, which customers can depend on through phone and email, as well as software updates. Take advantage of our 40 years of experience in delivering high-performance radar, communications, SIGINT, EW, and data acquisition MIL-Aero solutions worldwide.

### mercury

#### **Corporate Headquarters**

50 Minuteman Road Andover, MA 01810 USA +1 978.967.1401 tel +1 866.627.6951 tel +1 978.256.3599 fax

#### International Headquarters Mercury International

Avenue Eugène-Lance, 38 PO Box 584 CH-1212 Grand-Lancy 1 Geneva, Switzerland +41 22 884 5100 tel Learn more Visit: mrcy.com/go/MP57610 For technical details, contact:

mrcy.com/go/CF57610

The Mercury Systems logo and the following are trademarks or registered trademarks of Mercury Systems, Inc.: Mercury Systems, Innovation That Matters, Cobalt, GateFlow, and ReadyFlow. Other marks used herein may be trademarks or registered trademarks of their respective holders. Mercury believes this information is accurate as of its publication date and is not responsible for any inadvertent errors. The information contained herein is subject to change without notice.

© 2023 Mercury Systems, Inc. 1-0-031623-DS-C57610/58610